Applications:

|

|

Features:

|

|

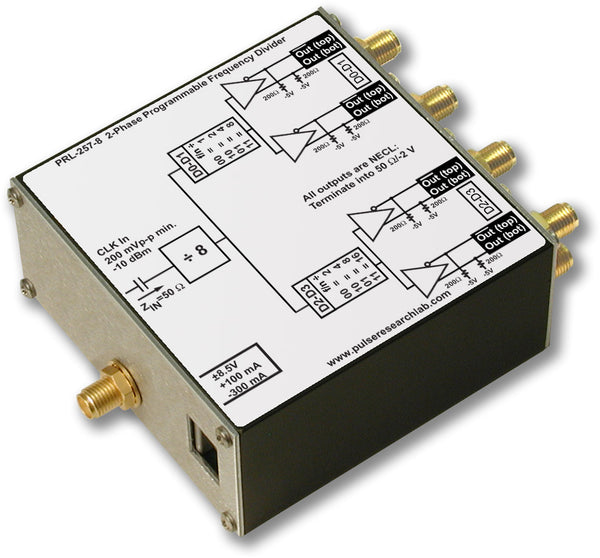

DescriptionThe PRL-255N is dual-channel NECL frequency divider module containing ÷2 and ÷4 frequency divider channels capable of toggling at frequencies in excess of 3 GHz. The two channels can be cascaded to provide a ÷8 function. The PRL-255N is an essential lab tools for device test and systems integration in wireless and digital communications applications. Each divider in the PRL-255N has differential inputs and complementary outputs. A common switch selects either single-ended or differential inputs. In the differential input mode, both inputs CLK and CLK are terminated internally into 50 Ω/VTT, and, therefore, either one or both inputs can accept AC coupled signals as well. In the single input mode, input signals should be connected to the CLK inputs only. The CLK inputs are internally switched to VBB, and input resistors RT for the CLK input channels are changed to 62 Ω. Complementary NECL outputs of both channels are designed for driving 50 Ω loads terminated into VTT. With internal pull-down resistors, these outputs can also be AC coupled for driving 50 Ω loads terminated to ground or to other voltages, such as LVPECL circuits. A block diagram of the PRL-255N is shown in Fig. 1. The PRL-255N is housed in a 1.3 x 2.9 x 2.2-in. extruded aluminum enclosure and supplied with a ±8.5 V/1.8 A AC/DC Adapter. |

PRL-255N Block Diagram

SPECIFICATIONS (0° C ≤ TA ≤ 35° C)*

| Symbol | Parameter | Unit | Min | Typ | Max | Comments |

|---|---|---|---|---|---|---|

| RIN | Input Resistance | 49.5 | 50 | 50.5 | Ω | |

| VTT | D Input Termination Voltage (fixed) | -2.2 | -2 | -1.8 | V | |

| VT | D Input Termination Voltage (variable) | -1.17/ -2.2 |

-1.3/ -2 |

-1.43/ -1.8 |

V | |

| VIL | Input Lo Voltage | -1.95 | -1.6 | -1.48 | V | |

| VIH | Input Hi Voltage | -1.13 | -0.9 | -0.81 | V | |

| VOL | Output Lo Voltage | -1.95 | -1.7 | -1.48 | V | |

| VOH | Output Hi Voltage | -1.13 | -0.9 | -0.81 | V | |

| IDC | DC Input Current | -265 | -250 | mA | ||

| VDC | DC Input Voltage | -12 | -8.5 | -7.5 | V | |

| VAC | AC/DC Adapter Input Voltage | 103 | 115 | 127 | V | |

| tPLH(÷2) | Propagation Delay to output↑ | 1.1 | 1.5 | ns | ||

| tPHL(÷2) | Propagation Delay to output↓ | 1.1 | 1.5 | ns | ||

| tPLH(÷4) | Propagation Delay to output↑ | 1.25 | 1.65 | ns | ||

| tPHL(÷4) | Propagation Delay to output↓ | 1.25 | 1.65 | ns | ||

| tr/tf | Rise/Fall Times (20%-80%) | 325 | 425 | ps | Note (1) | |

| tSKEW | Skew between Q & Q outputs | 20 | 75 | ps | ||

| FMAX | Max clock frequency | 2.5 | 3.2 | GHz | Note (3) | |

| VCMR | Common Mode Range | -2.7 | -0.4 | V | Note (2) | |

| Size | 1.3 x 2.9 x 2.2 | in. | ||||

| Shipping weight, incl. AC adapter | 4 | lb. | ||||